友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

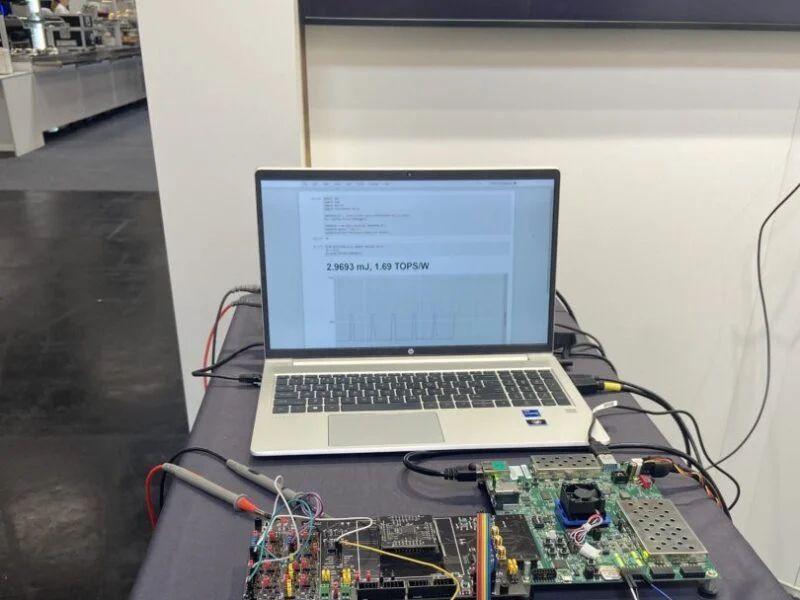

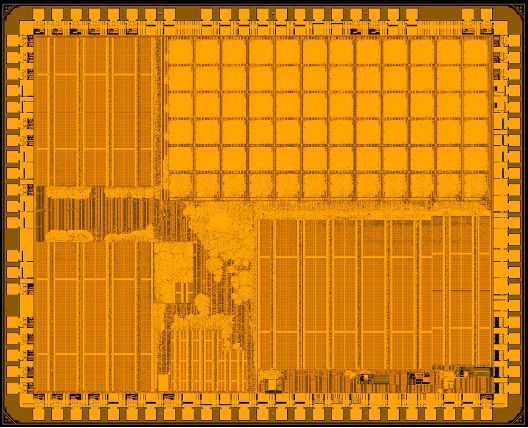

全新 AI 处理器设计可实现功耗不变,性能提升 10-100 倍

77

0

相关文章

近七日浏览最多

最新文章

标签云

卡内基

斯图尔特

美俄

java

梅隆大学

加拿大

凯蒂

阿汤哥

美国历史

情到深处

哥伦比亚大学

伯克利音乐学院

克鲁斯

人际关系

任天堂

游戏

处理器

kimi

阿里

俄罗斯

航空航天

谷歌

人工智能

黎明之前

教父

end

http

黑客

行星

太阳系

ddos

高通

联发科

arm

自研芯片

小米集团

智能手机

知名企业

华为

说句实话

骁龙至尊版

台积电

白手套

芯片领域

酷睿

硬盘

主机

内存

性价比

mini

电池容量

soc

骁龙

华为公司

华为手机

oled

国产品牌

se

英特尔

微星

vivo

小米

小米公司

防水

apple

苹果

iqoo

npu

gpu

cpu

天风证券

归母净利润

英特尔酷睿

更上一层楼

ultra

酷睿处理器

显卡

千元机

联发科天玑

安卓

redmi

ois

reno

毛利率

荣耀10

写真

小米mix

红米手机

usb30

独立显卡

绝地求生

初创公司

机器人

微软

街拍

星二代

巨蟒

学院

高跟鞋

板块

小鲜肉

北京化工大学

苹果公司

创新工场

李开复

微软公司

alphabet

中国学生

芯片

复旦大学

香港大学

美国

我们这一代