友情提示

本站部分转载文章,皆来自互联网,仅供参考及分享,并不用于任何商业用途;版权归原作者所有,如涉及作品内容、版权和其他问题,请与本网联系,我们将在第一时间删除内容!

联系邮箱:1042463605@qq.com

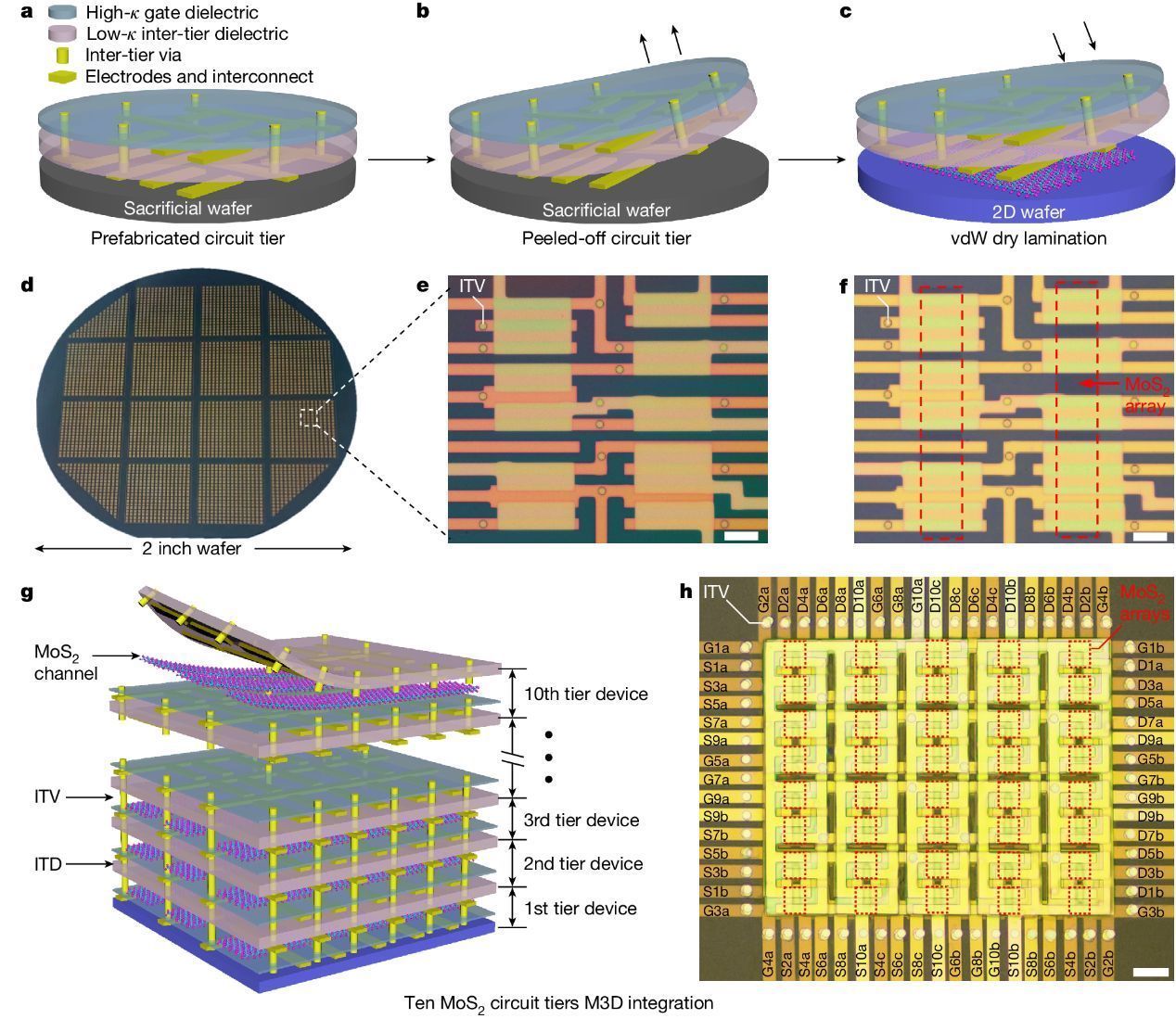

实现 10 层单芯片三维系统,湖南大学团队新成果登《Nature》

40

0

相关文章

近七日浏览最多

最新文章

标签云

刘渊

三国志

刘备

罗贯中

中山靖王

nature

芯片

mina

湖南大学

鲜卑

东晋

慕容氏

羯族

中国历史

匈奴人

汉人

五胡乱华

胡人

游牧民族

刘弗陵

果糖

水果

蔗糖

癌症

脱酸剂

柠檬酸

砂糖橘

骨质疏松症

哺乳期

rain

加州大学

机器学习

谷歌公司

天气预报

谷歌

复旦大学

美元

睡眠质量

仿制药

2型糖尿病

南京中医药大学

高校

新京报

上海大学

科学家

爱因斯坦

华中科技大学

蚊子

蛋白质

清华大学

清华

癌细胞

上海交通大学

肿瘤

上海交大

西北大学

太阳

美国国家航空航天局

nasa

心血管疾病

不饱和脂肪酸

胆固醇

血管

饮食

同型半胱氨酸

叶酸

日本

女团

韩国女团

剑桥大学

oled

大数据

北京互联网法院

人工智能

黄仁勋

英伟达

显卡

首席执行官

美国商务部

半导体

商务部

药品

中国

白宫

美国

美媒

科技巨头

海湖庄园晚宴

唐纳德特朗普

荷兰

碳化硅

德国

外交部

林剑

nsa

grok

埃隆_马斯克

deepseek

豪威

雷军

微电子

民营企业家

华为

欧洲

知名企业

英伟达gpu

国际消费电子展

微软

nvidia

OpenAI

疯狂

贝尼奥夫

gpu

钛媒体

a100

大语言模型

算法

老子

代码

微星

非公版

rtx

系列显卡

字节跳动

blackwell

内存条

性价比

颗粒ddr5

垄断

烟草

张泉灵

华为手机

骁龙至尊版

华为mate

周一

拜登政府

出口限制

乔拜登

互联网协会

国家安全

多核

余承东

高通骁龙

全大核架构

mate70

市场份额

手机

高通

性能

骁龙8gen2

逮捕

间谍罪

反间谍法

韩国公民

三星电子

显示屏

苹果公司

apple

ipadmini

熊彼特

刘向明

经济危机

资本主义

医疗免费

子夏

欧阳

张超

李治廷

张海潮

中国梦

批量

英伟达ceo

间谍

情报机关

国家安全部

eco

基准利率

mac

韩国央行

韩国

美股

亚马逊

英特尔

cpu

日元

铃木汽车

三菱重工

instagram

游泳

奥运会

煤炭

chris

linux

ows

gdp

lpr

恒生指数

央行

通胀率

路透社

日本央行

初创公司

金融科技

摇滚乐队

花花公子

互联网时代

a股

特斯拉

超级工厂

消费税

欧盟

巴尔韦德

皇马

国防部

se

黄埔

电动自行车

外卖

外卖小哥

凯迪拉克

投资

犯罪心理

加西亚

阿尔维斯

刘易斯

robert

指数

股份

vivo

智能手机

三星

银监会

民营银行

中信证券

其他

岳麓山

爱晚亭

岳麓书院

山麓

枫林

中国人民大学

中国科学院大学

长沙

大连理工大学

雷锋

广西

金融知识

中南大学

投档分数线

985高校

华东五校

西工大

哈工大

投档线

南京大学

就业

博士

学位

吴丹红

论文抄袭

大学副教授

矿产资源

世界500强

历史文化

空气质量

生态文明

学院

北京大学

北京航空航天大学

科技

湖南省

nlp

云计算

阿里云

学生时代

师范专业

医保

交通银行

社保

乘风破浪

中国农业大学

吉林大学

中央民族大学

归母净利润

中泰证券

重庆

动力电池

半导体产业

光刻机